TUGAS

MODUL 5

FLIP FLOP

DISUSUN OLEH :

ELLY ASTUTI FERA ROSITASARI

123090075

PLUG 2

ASS : JEFRI SENOAJI

JURUSAN TEKNIK INFORMATIKA

FAKULTAS TEKNOLOGI INDUSTRI

UNIVERSITAS PEMBANGUNAN NASIONAL [V] YOGYAKARTA

TUGAS

ü Mengapa pada RS Flip – flop dengan clock dari hasil Q dan Q’ berubah – ubah?

Input Clock merupakan input kontrol yang akan mengatur nilai R dan S yang masuk ke Flip-flop. Jika Clock bernilai 1, output Flip-flop akan berubah ke kondisi Next-nya sesuai dengan kombinasi input R dan S nya. Jika Clock bernilai 0, output Flip-flop tidak berubah, artinya kondisi Next sama dengan kondisi Present-nya, atau . Dengan kondisi ini maka flip-flop dapat dikatakan sebagai elemen penyimpan.

ü Skema Master Slave Flip – flop dan IC yang digunakan :

Skema pengkabelan menggunakan IC 7472

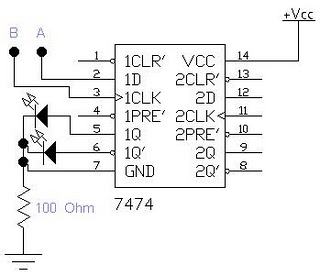

Skema pengkabelan menggunakan IC 7474

IC yang digunakan yaitu IC 7472 dan IC 7474

0 komentar:

Posting Komentar